-

Book Overview & Buying

-

Table Of Contents

LLVM Code Generation

By :

Sign In

Start Free Trial

Sign In

Start Free Trial

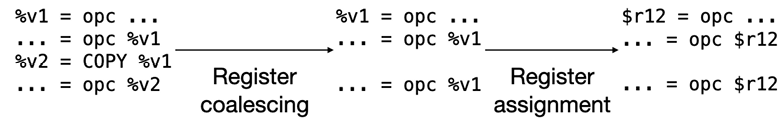

In LLVM, register allocation is split into two main optimization passes in the machine pass pipeline. More specifically, after eliminating the static single assignment (SSA) form of the input program during the PHI-elimination pass, as you learned in Chapter 13, LLVM performs the register coalescing phase and, later, the register assignment phase. The coalescing phase consists of merging variables connected by a COPY instruction together. The assignment phase consists of replacing the virtual registers with physical registers or memory locations. Figure 19.1 illustrates these two phases, while Figure 19.2 illustrates the register allocation process in LLVM:

Figure 19.1: The role of the register coalescing and register assignment phases

Figure 19.1 demonstrates how the register coalescing phase simplifies the Machine intermediate representation (IR) by merging the %v1 and %v2 variables. Thanks to this coalescing, the COPY instruction...